The members of an orchestra are often great virtuosi on their own instruments, but the conductor - the maestro – is equally important. The maestro has his score on the conductor’s stand to know exactly what is supposed to be played. He explores the individual intonation and assembles the orchestra into a unique sound. Most importantly, he has to verify that every single tone fits the master plan – the score of the musical composition.

Virtuoso ADE Verifier

There is a third product besides Virtuoso ADE Explorer and Virtuoso ADE Assembler in the new ADE tool group – Virtuoso ADE Verifier. Let’s check out what it is good for and how to get started quickly – in fact in 3 minutes to make it a bit of a challenge!

You may have seen the introduction material on ’The New Sound of Analog Design’. There is more material to help you get started (links below), if you happen to have more than 3 minutes.

Verifier in 3 Minutes

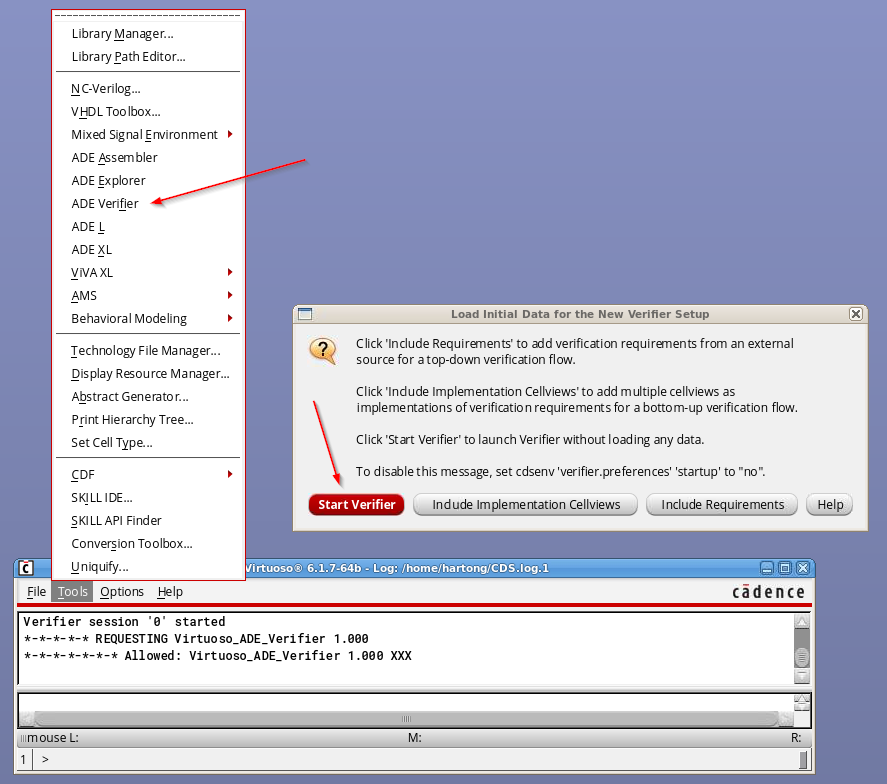

Open Virtuoso IC6.1.7 in your current working area. Go to ‘Tools / ADE Verifier’ from the CIW to launch the new verification tool. You can skip over the initial dialog by clicking ‘Start Verifier’. Et voilà – Verifier is up.

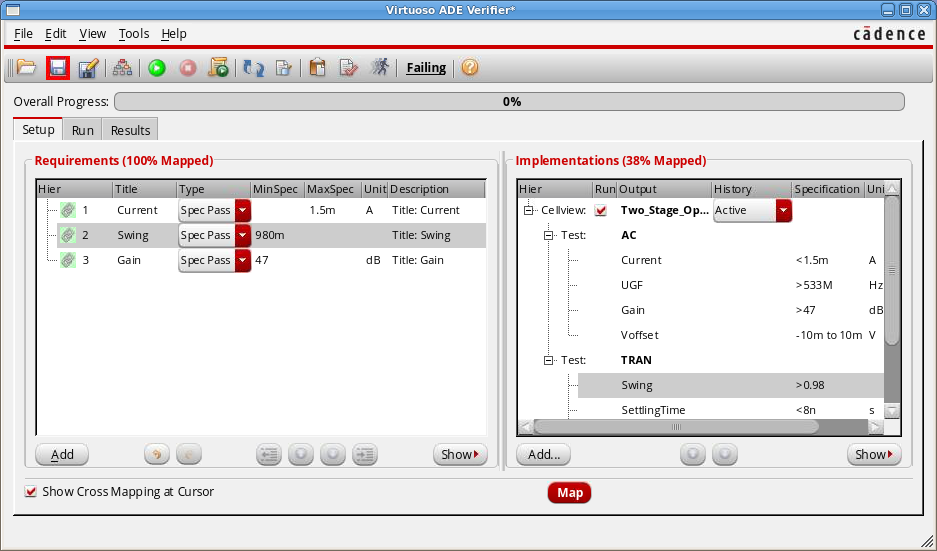

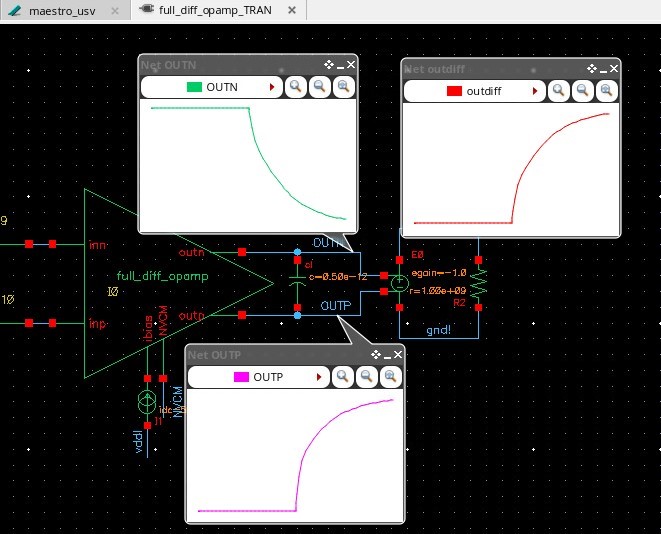

Now we should enter our verification requirements – but let’s skip that and instead work bottom-up! Find the ‘Add…’ button located at the bottom of the ‘Implementations’ panel. Browse and select a suitable ADE or a new ‘maestro’ cellview if you have one. If you pick an ADE state, Verifier will automatically convert it into a new ‘maestro’ cellview. What is ‘suitable’? Well, select something small with a few measurements and spec for now.

In the ‘Implementations’ panel, multi-select everything you find important, click the right mouse button, and select ‘Create Requirements’. Two things happen now: (1) new requirements are created from the selected implementations, and (2) the new requirements are mapped to their corresponding implementations. Hover your mouse over some implementations or requirements – do you see the mapping?

The structure and content of our verification plan isn’t great but we have to compromise for our ‘3 minute goal’. I’m sure you will find out how to add new entries to the plan, change the hierarchy, and edit the description of the entries.

1 Minute Remaining!

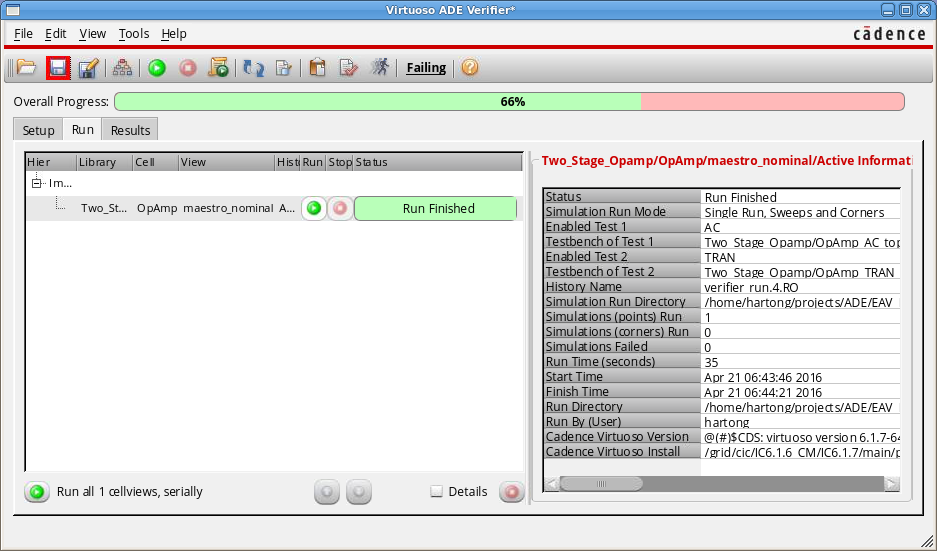

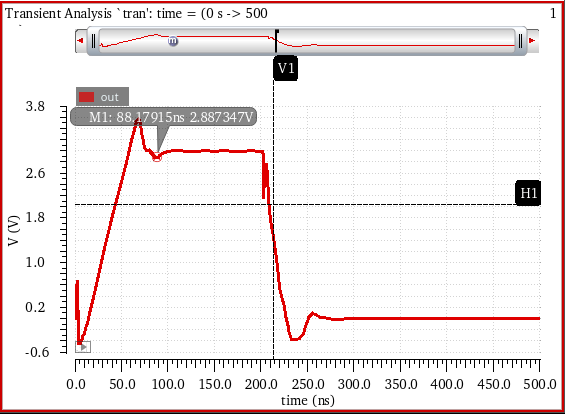

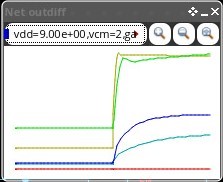

Move over to the ‘Run’ tab and click the green run button. Now, Explorer/Assembler will be running in the background and hopefully give you a nice ‘Run Finished’ feedback soon. Spend 10 seconds to review the right-hand side information on the ‘Run’ tab before you move over to the ‘Results’ tab.

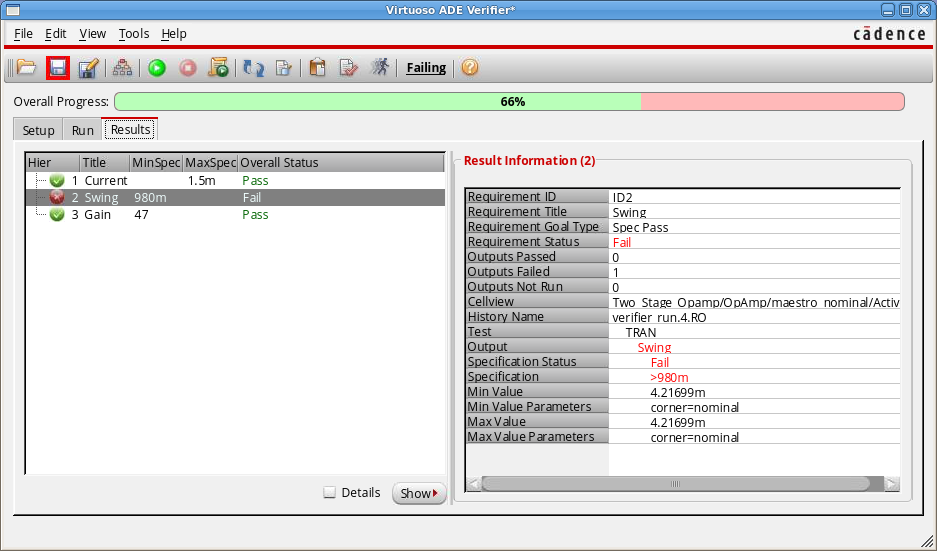

Here you should see your requirements with the pass/fail status attached to it. Spend another 10 seconds to review the right-hand side again. Save your new Verifier cellview for later.

… And – time over 2:59 – great job!!!

So what?

Have you gained any additional design/verification information in these 3 minutes? Probably not, but remember the orchestra. Hiring a conductor for your harmonica playing at home would be pretty silly, wouldn’t it? But think if you could get an overview of all your simulation results for the current project. Now assume you could have an overview of the results of the whole team and finally assume you have a precise verification plan telling you exactly what you need to do, what you have done already and what is missing. Wouldn’t this make you the maestro of your own analog verification project?

Did you make this journey in 3 minutes? Drop us a comment below. Your questions and ideas are welcome too.

TeamADE

More Info

For more details, take a look at the following videos and material:

Whitepaper:

Videos:

- Verifier introduction

- Using batch scripts for Verifier

- Verifier RAK getting started

- Verifier RAK basic flow